three-stage op-amp

Looking at this in 2020, this is one of the worst amplifiers I have ever made, but we still got an A on this project—please do not think this is the extent of my capability.

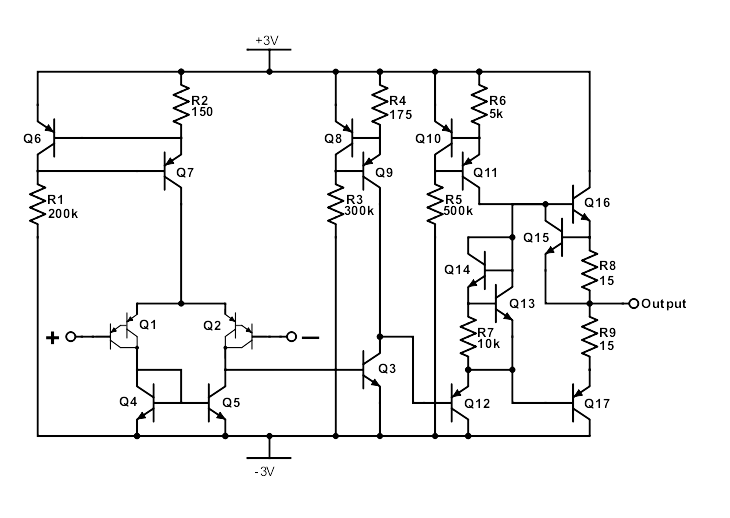

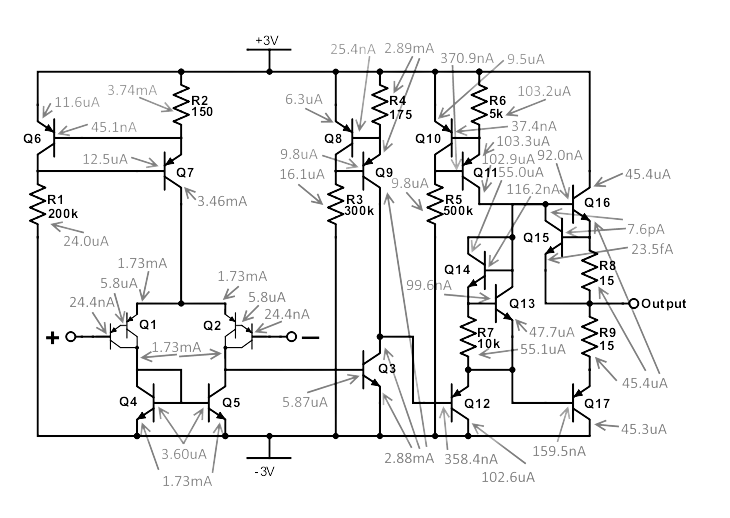

Schematic

Throughout this amplifier, we alternate PNP and NPN stages to maintain headroom without using an explicit, ”battery-based” level shifter, i.e, a resistor in series with a current source in the signal path, which would decrease common-mode range.

input stage

The input stage of this op-amp is a PNP differential pair (Q1, Q2) with Darlington inputs and current mirror load (Q4, Q5, R1, R2). The tail current is set by the base-emitter referenced current source comprising Q6, Q7, R1, and R2. Because the output current is set by the voltage drop over R2, which is set by Q6 to be Veb,6, the current is determined overwhelmingly by \(V_{eb,6}\), which is highly stable with respect to \(i_C\) (varies exponentially with \(i_C\)). Additionally, this stability is enhanced by by Q7, which, by the same principle, protects the current from variation in the opposite supply. It also increases the mirror’s output impedance and provides feedback, protecting against mismatch variation.

The PNP Darlington inputs decrease the input current draw by a factor of \(\beta\), functioning as a single transistor with an effective \(\beta\) of approximately \(\beta_{PNP}^2\), though we do sacrifice some headroom, since the |\(V_{be}\)| must be twice that of a single transistor in order for both transistors to be on. The introduction of the Darlington inputs allowed the op-amp to have input bias currents well under 100nA per input.

The basic NPN current mirror load on the input stage mirrors the current from the noninverting input to the output of the first stage, performing differential to single-ended conversion without sacrificing half the differential gain.

The first stage is built with PNP active transistors due to the common-mode range of -2V to 1V. The current source for this stage was placed at the top rail to take advantage of the 2V headroom (from 3V to 1V), leading to the choice of PNP for the gain elements and NPN for the current mirror load.

gain stage

The gain stage of this amplifier is a basic NPN common-emitter (Q3) with an active base-emitter referenced current source (Q8, Q9, R4, R3) load, which, as discussed previously, has a high output impedance and therefore allows the gain of this stage to be high The common-emitter stage provides high gain:

\[ A_{v,S2} = −g_{m,3}(R_{o,CM}||R_{in,S3}) \]

with \(R_{o,CM}\) indicating the current mirror’s output impedance and \(R_{in,S3}\) indicating the input impedance of the output stage. however, since the gain is inverting, the Miller effect applies to the parasitic capacitance \(C_{bc,3}\), which sees \(R_{π,3}||R_{o,2}||R_{o,5}\), forming a high-impedance node and limiting bandwidth.

output stage

The output stage is a Class AB output stage with partial output short protection provided by Q15: when the current through R15 is sufficient to cause a Vbe voltage drop across R8, Q15 turns on, robbing Q16 of its base current and thereby limiting total output current to \(\frac{V_{be}}{R_8}\)

Q13, Q14, and R7 work to maintain a voltage drop of \(2V_{be}\) while decreasing the quiescent current through Q16 and Q17. By setting \(I_{C,14} < I_{C,13}\), which can be done by setting \(I_{C,14} = \frac{V_{be,13}}{ R_7} < I_{C,13}\), the quiescent current through Q16 and Q17 can be decreased significantly.Though this amplifier does not do that, only 14.4μA run through Q16 and Q17. Because Q14 and Q13 are hooked up in feedback, this biasing technique is still useful: it provides a stable voltage drop of approximately \(2V_{be}\).

Specifications Current Consumption

| \(A_v\) | 110.3 dB = 327.3 V/mV |

| \(\omega_u\) | 113 MHz |

| Max. Current Consumption | 6.55 mA at -2.6V CM |

| Max. Input Bias Current (Per Input) | 25.7 nA at -2.6V CM |

| Input CM Range | -2.6V to 1.2V |

| Output Short Protection (Positive Swings) | 34.1 mA with grounded output |

| Offset Voltage | -236 µV |

| Gain Required for Stability (45◦ phase margin) | Decrease of 40 dB |

| Input Impedance | 23.4 MΩ at DC |

| Output Impedance | 36.2 Ω at DC |

| Slew Rate | 354.0 V/μs |

The gain response of the op-amp over the -2V to 1V common-mode range.

The open-loop AC gain and phase response of the op-amp with a 0V common-mode input, showing that the gain needs to be decreased by 40dB to attain marginal stability.

A DC sweep of the noninverting input with the inverting input grounded, showing the offset voltage of the op-amp to be -236μV.

{A plot of the op-amp's input impedance, from DC to the unity-gain frequency and beyond.

A plot of the op-amp's output impedance, from DC to the unity-gain frequency and beyond.

A transient simulation of a 1V step with no rise time input applied to the op-amp in unity-gain configuration, showing instability.

A transient simulation of a 1V step with no rise time input applied to the op-amp in feedback configuration with a gain of 2.2, showing a 2.5% overshoot and a phase margin around 68°, if you ignore the apparent bandwidth limiting

A transient simulation of a 100µV step with 10ns rise time input applied to the op-amp in unity-gain configuration, showing an overshoot of 20.5\% and a phase margin of approximately 48°. Included to show a non-bandwidth-limited step-response.

A transient simulation of a 500mV step input applied to the op-amp with a gain of -1 in feedback, showing instability.

A transient simulation of a 500mV step input applied to the op-amp with a gain of -2 in feedback, showing instability.

A transient simulation of a 500mV step input applied to the op-amp with a gain of -10 in feedback, showing stability on both ends.

The same transient simulation of a 500mV step input applied to the op-amp with a gain of -10 in feedback, showing a slew rate of 354.0 V/µs.